#### **OPEN ACCESS**

# Electrode dependent interfacial layer variation in metal-oxide-semiconductor capacitor

To cite this article: I-S Park et al 2014 IOP Conf. Ser.: Mater. Sci. Eng. 54 012004

View the article online for updates and enhancements.

# Related content

- Direct Comparison of ZrO<sub>2</sub> and HfO<sub>2</sub> on Ge Substrate in Terms of the Realization of Ultrathin High- Gate Stacks Yoshiki Kamata, Yuuichi Kamimuta, Tsunehiro Ino et al.

- Experimental investigation of interfacial and electrical properties of post-deposition annealed Bi2Mg2/3Nb4/3O7 (BMN) dielectric films on silicon B S Sahu, Jun-Ku Ahn, Cheng-Ji Xian et al.

- Physical and Reliability Characteristics of Metal-Oxide-Semiconductor Devices with HfO\_N\_Gate Dielectrics on Different Surface-Oriented Substrates Chin-Lung Cheng, Kuei-Shu Chang-Liao, Ping-Liang Wang et al.

### Recent citations

- GeOx interfacial layer scavenging remotely induced by metal electrode in metal/HfO2/GeOx/Ge capacitors Taehoon Lee et al

- Peculiarities of the Interface between High-Permittivity Dielectrics and Semiconductors Nenad Novkovski

# Electrode dependent interfacial layer variation in Metal-Oxide-Semiconductor capacitor

I-S Park<sup>1,2</sup>, Y C Jung<sup>1</sup>, M Lee<sup>1</sup>, S Seong<sup>1</sup>, and J Ahn<sup>1</sup>

- <sup>1</sup> Department of Materials Science & Engineering, Hanyang University, Seoul, Korea

- <sup>2</sup> Institute of Nano Science and Technology, Hanyang University

- 222 Wangsimni-ro, Seongdong-gu, Seoul 133-791, Korea

E-mail: jhahn@hanyang.ac.kr

**Abstract.** The interfacial layer between oxide and semiconductor in metal-oxide-semiconductor (MOS) capacitors depends on the metal electrode material. The metal/HfO<sub>2</sub>/Si and metal/HfO<sub>2</sub>/Ge capacitor were made using an atomic layer deposited HfO<sub>2</sub> dielectric films and Mo, Ru, and Pt electrodes above Si substrate and Ti, Ru, and Pt electrodes above Ge substrate. The measured saturation capacitance was varied with electrode and evaluated to capacitance equivalent thickness (CET). In Si-based MOS capacitor, the CET value of the capacitor with Pt electrode is larger than those with Mo and Ru electrode. In addition, the CET is 27.4 A, 38.2 A, and 30.8 A for Ti, Ru, and Pt electrode, respectively, for Ge-based MOS capacitors. The CET variation with electrode is attributed the variation of dielectric constant of HfO<sub>2</sub> dielectric and the difference of interfacial layer. The CET variation is well in agreement with the interfacial layer thickness taken by a transmission electron microscopy. The thickness variation of interfacial layer results from the oxygen gettering ability of the electrode even though they are apart.

# 1. Introduction

Si-based metal-oxide-semiconductor (MOS) transistors have faced a challenge for continuous and exponential scaling-down of feature size. With this rapid scaling of MOS transistors, that is, the decrease of channel length and gate dielectric thickness, new materials, processes, and structures have been introduced to the IC manufacturing industry [1]. As new materials, high-mobility channels, high dielectric constant (k) gate dielectrics, and metal gate electrodes are under research and development to replace Si channel, SiO<sub>2</sub> dielectric, and doped-polycrystalline Si electrode, respectively. With the successful introduction of high-k and metal gate (HKMG) beyond 45 nm technology [2, 3], high mobility channels such as Ge and GaAs have been focused as a further solution for the carrier mobility enhancement in logic devices. On the high-k/semiconductor interface, the native oxide, playing a role of additional dielectric with high-k oxide, is a layer to decrease the capacitance of MOS transistor. With scaling-down of devices, the interfacial native oxide should be controlled and reduced for higher capacitance [4, 5]. When the devices are processed with the same high-k deposition and post-annealing, the capacitance of capacitor is strongly dependent on the metal electrode materials. The value of capacitance is easily compared in term of equivalent oxide thickness (EOT) or capacitance equivalent thickness (CET). The electrode dependent CET of capacitor has also been reported [6, 7].

Content from this work may be used under the terms of the Creative Commons Attribution 3.0 licence. Any further distribution of this work must maintain attribution to the author(s) and the title of the work, journal citation and DOI.

IOP Conf. Series: Materials Science and Engineering 54 (2014) 012004

doi:10.1088/1757-899X/54/1/012004

Atanassova *et al.* reported the EOT and dielectric constant variation of Ta<sub>2</sub>O<sub>5</sub> MOS capacitors with Al, Au, W, TiN, and TiN/W electrodes, and suggested that these variations are related to the gate electrode/Ta<sub>2</sub>O<sub>5</sub> interaction during electrode deposition [6]. Kim *et al.* also reported the EOT decrement of HfO<sub>2</sub> and ZrO<sub>2</sub> MOS capacitors when Ti is used as a top electrode compared to those of Al and Pt, and claimed that this decrement comes from the decomposition of the SiO<sub>2</sub> interfacial layer between high-k dielectric and Si substrate [7].

Atomic layer deposition (ALD) has been widely employed to making high-k gate oxides [1, 4, 5]. In ALD, the film grows through a self-limiting surface reaction between precursors that are alternately supplied into a substrate. The precursors are separated by inert gas purging to remove the physisorbed precursor and to block the gas-phase reaction between precursors. Even though the ALD method has the disadvantage of low growth rate, it offers high-quality thin films, excellent atomic-level thickness controllability and uniformity in a wide surface, high conformality, and excellent repeatability.

Metal for gate electrode applications requires a suitable work function and thermal stability [8, 9]. Single metal electrodes with a higher work function similar to conduction band such as Pt and Ru are the promising candidates for p-MOS devices and that with a lower work function similar to valence band such as Ti are for n-MOS. Mo electrode has applied for p-MOS, n-MOS and midgap devices. In this work, the capacitance variations of both Si- and Ge-based MOS capacitors were investigated with the structures of metal/ALD-HfO2/Si and metal/ALD-HfO2/Ge using capacitance-voltage (C-V) measurements. The capacitance was dependent on a metal electrode even though the capacitors were processed indentically except for the electrode specimen. To investigate the structural status of interfacial layers concerning to this capacitance variation, cross-sectional transmission electron microscopy (TEM) analyses were also conducted.

# 2. Experiments

The substrates used in this study were p-type (100) Si wafers with B of  $3 \times 10^{15}$  atoms/cm<sup>3</sup> doping concentration and p-type (100) Ge wafers with Ga of 4.5 × 10<sup>17</sup> atoms/cm<sup>3</sup> each other. Prior to HfO<sub>2</sub> deposition on Si wafers, standard RCA cleaning with final 100:1 HF-dip for 10 sec was performed to remove the native oxide and also on Ge wafers, wet chemical cleaning was performed with 100:1 HF dipping, followed by DI water rinse for five cycles [10]. High-k HfO<sub>2</sub> dielectric films were deposited in a travelling-wave type ALD reactor (made by CN1) using a liquid Hf[NCH<sub>3</sub>C<sub>2</sub>H<sub>5</sub>]<sub>4</sub> precursor and H<sub>2</sub>O oxidant. Hf precursor was volatilized from the canister heated at 60°C and was carried into the reaction chamber with a carrier gas of N<sub>2</sub>. Nitrogen was also used as a purge gas. The canister containing H<sub>2</sub>O was kept at room temperature and no carrier gas was used to deliver it to the ALD reactor due to its high vapor pressure. After HfO<sub>2</sub> film deposition, square-type gate pattern was defined using a conventional photolithography process. And then, top electrodes such as Mo, Ru, Pt, and Ti were deposited on HfO2 film and photoresist by a DC magnetron sputtering system at room temperature. In case of Ti electrode, Pt was also stacked on it to prevent its surface oxidation. The base pressure of the sputter system was less than  $2 \times 10^{-6}$  torr and deposition was performed at  $3 \times 10^{-6}$ 10<sup>-3</sup> torr. The back surfaces of the substrates were metallized to provide ohmic contact to semiconductor substrate for electrical measurements. The fabricated MOS capacitors were treated by forming gas anneal (FGA) for 30 min in N<sub>2</sub> ambient with 5 % H<sub>2</sub> at 400 °C.

The C-V measurements were performed in parallel mode at 1 MHz frequency using a HP4284 LCR meter by sweeping from 2 V to -2 V. For the cross-sectional analyses for the interfacial layer (IL), TEM measurements were performed for all MOS capacitors.

#### 3. Results and Discussion

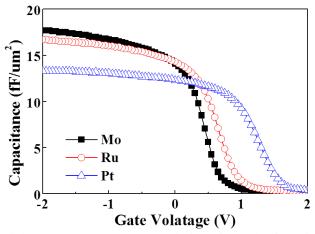

Figure 1 shows the typical C-V curves of metal/HfO $_2$ /Si MOS capacitors with Mo, Ru, and Pt metal electrodes. The physical thickness of high-k HfO $_2$  on native oxide is the same 5 nm. The saturated capacitance at -2 V could be evaluated into CET for comparison and the measured CET is 19.5 A, 20.7 A, and 26.0 A for Mo, Ru, and Pt electrode, respectively. It is observed that the CET value of the capacitor with Pt electrode is larger than those with Mo and Ru electrode, even though all capacitors

were processed indentically except for the material specimen of metal electrode. Another apparent feature is the shift of C-V curves with metal electrode material. The C-V curve of capacitor with Pt electrode is much shifted positive direction with respect to those with Mo and Ru electrode. The shift of C-V curves is relatively in agreement with the work function variation of the metal materials [4].

**Figure 1.** Electrode material dependent C-V characteristics of metal/HfO<sub>2</sub>/Si MOS capacitors with Mo, Ru, and Pt electrode, respectively. The high-k HfO<sub>2</sub> films are 5 nm thick.

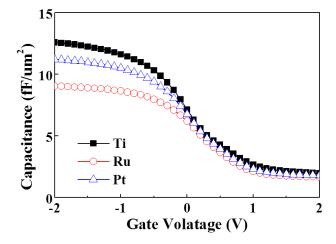

In addition, Fig. 2 shows the typical C-V curves of metal/HfO<sub>2</sub>/Ge MOS capacitors with Ti, Ru, and Pt metal electrodes. These curves of Ge-based MOS capacitors are very different with those of Si-based capacitors in Fig. 1. It is found a stretch-out in the C-V curve meaning many interfacial traps and a higher value of in the inversion region indicating an additional and parasitic capacitor generated near a Ge substrate. On the parasitic capacitance at inversion region for capacitors with Ru electrode, Cmin/Cmax for Si capacitor is 1.8 % but that for Ge is 18.2 % where Cmin is the minimum capacitance and Cmax is the maximum. These results indicate the unstable GeO<sub>x</sub> interfacial layer formation on Ge substrate. It is also observed the saturated capacitance at -2 V is dependent on the metal electrode and the measured CET is 27.4 A, 38.2 A, and 30.8 A for Ti, Ru, and Pt electrode, respectively. Interestingly, the CET value of the capacitor with Ru electrode is larger than that of Pt electrode. It is the opposite result with that for Si substrate. For the shift of C-V curves, it is very little in case of Ge substrate due to the Fermi level pinning [11].

**Figure 2.** Electrode material dependent C-V characteristics of metal/HfO<sub>2</sub>/Ge MOS capacitors with Ti, Ru, and Pt electrode, respectively. The high-k HfO<sub>2</sub> films are 5 nm thick.

doi:10.1088/1757-899X/54/1/012004

As the capacitance of simple capacitor is expressed in form of C = kA/d where k is the dielectric constant of dielectric, A is the effective area of capacitor, and d is the thickness of dielectric. And, CET can be evaluated as  $CET = 3.9A/C_m$ , where k of  $SiO_2$  is 3.9 and  $C_m$  is the measured capacitance in maximum. When three dielectrics are stacked in parallel, the total  $CET = CET_1 + CET_2 + CET_3$ , where  $CET_n$  is CET of n-th dielectric. In the MOS capacitor, usually, three dielectric layers are can be supposed, that is, 1) the bottom IL between oxide and semiconductor, 2) main dielectric (it will be denoted as dielectric), and 3) the top IL between metal and oxide.

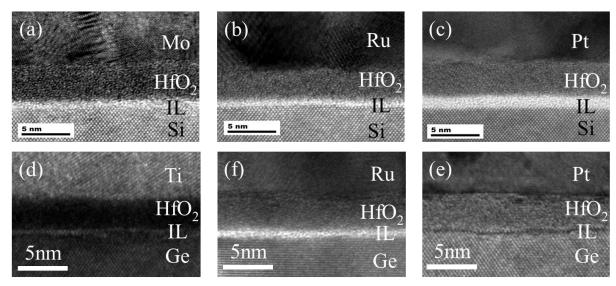

To identify ILs and dielectric affecting to capacitance variation with metal electrode, TEM images of MOS capacitors were taken as shown in Fig. 3. It is found that the Ge surfaces under bottom IL are much rougher than Si surfaces due to the softness of Ge against wet HF chemical. At first, it is observed that top ILs show rough surface compared to bottom ILs but there is not so apparent layer in all images in Fig. 3. For the HfO<sub>2</sub> dielectrics, their structures were not crystallized on Si and Ge substrates due to the low thermal budget. Their values of dielectric constant on Si are 17.7, 18.8, and 23.2, respectively, which were evaluated from the relationship between EOT and the physical thickness of HfO<sub>2</sub> films [4]. Considering the dielectric constant of HfO<sub>2</sub>, for example 17.7, the contribution of HfO<sub>2</sub> film with 4.5 A (k(HfO<sub>2</sub>)/k(SiO<sub>2</sub>)) corresponds to 1 A of CET. The higher the dielectric constant of HfO<sub>2</sub> is, the lower its contribution to CET is. This result indicates that the dielectric constant of dielectric is strongly dependent on the top metal electrode. This dependence comes from the deposition process of electrode and post-annealing [6], which attribute to the inter-diffusion of elements in both dielectric and electrode.

For the bottom ILs, they show obviously different thickness in the TEM images with electrode. In case of Si substrate, the IL with Pt electrode is about 15 A whereas those with Mo and Ru electrodes are about 7-8 A. This difference is well in agreement with the difference of CET in Fig. 1. For Ge substrate, the ILs below Ti and Pt are much thinner than IL below Ru, so that CET of the capacitors with Ti and Pt result in a lower value. Ti film as well as Ba, Ti, Zr, Hf, V, Nb, and Ta is well-known as one of oxygen-getter materials [12]. Assuming the gettering ability of Ti film whether it is apart with IL and so IL becomes thinner after electrode deposition and FGA, other metal layers such as Mo, Ru, and Pt can also getter the oxygen in ILs. However, the gettering effect is different with the specimen of bottom IL. For example, Ru film can getter the IL on Si but not much on Ge as shown in Figures. 3(b) and 3(f). It is found that Mo and Ru films are efficient at gettering oxygen from SiO<sub>2</sub> IL and Ti and Pt films are from GeO<sub>x</sub> IL. In addition, the oxygen gettering of electrode from the oxide film, HfO<sub>2</sub>, gives rise to variation of dielectric constant of dielectric film.

**Figure 3.** Cross-sectional TEM images of metal/HfO<sub>2</sub>/Si MOS capacitors with the electrode of (a) Mo, (b) Ru, and (c) Pt and metal/HfO<sub>2</sub>/Ge capacitors with (d) Ti, (e) Ru, and (f) Pt electrode, respectively.

IOP Conf. Series: Materials Science and Engineering 54 (2014) 012004

doi:10.1088/1757-899X/54/1/012004

#### 4. Conclusion

The electrode dependent ILs in MOS capacitors of metal/HfO<sub>2</sub>/Si and metal/HfO<sub>2</sub>/Ge are investigated by using C-V measurements and cross-sectional TEM analyses. The metal/ALD-HfO<sub>2</sub>/Si capacitors with Mo, Ru, and Pt electrode and metal/ALD-HfO<sub>2</sub>/Ge capacitors with Ti, Ru, and Pt electrode were fabricated. The measured values of CET were varied with electrode material. In Si-based MOS capacitor, the CET value of the capacitor with Pt electrode is larger than those with Mo and Ru electrode. In addition, the CET is 27.4 A, 38.2 A, and 30.8 A for Ti, Ru, and Pt electrode, respectively, for Ge-based MOS capacitors. The CET variation is attributed to the variation of dielectric constant of HfO<sub>2</sub> film and the thickness difference of IL. The CET variation is well in agreement with the thickness of ILs. Even though electrode and IL are apart, the oxygen-gettering of the electrode affects to IL. The choice of electrode is a promising approach to control the state of IL on semiconductor for the higher capacitance.

#### **Acknowledgments**

This work was supported by the IT R&D program of MOTIE (KI002083, Next-Generation Substrate Technology for High Performance Semiconductor Devices) and Basic Science Research Program through the National Research Foundation of Korea(NRF) funded by the Ministry of Education(2012R1A6A1029029).

# References

- [1] Wilk G D, Wallace R M and Anthony J M 2001 J. Appl. Phys. 89 5243

- [2] Veloso A, Hoffmann T, Lauwers A, Yu H, Severi S, Augendre E, Kubicek S, Verheyen P, Collaert N, Absil P, Jurczak M and Biesemans S 2007, *Sci. Technol. Adv. Mater.* **8** 214

- [3] Ishimaru K 2008 Solid-State Electron. 52 1266

- [4] Park I-S, Lee T, Ko H, Ahn J 2006 J. Kor. Phys. Soc. **49** S760

- [5] Park I-S, Choi Y, Nichols W T, Ahn J 2011 Appl. Phys. Lett. 98 102905

- [6] Atanassova E, Paskaleva A, Novkovski N and Georgieva M 2005 J. Appl. Phys. 97 094104

- [7] Kim H, McIntyre P Chui CO, Saraswat K C and Stemmer S 2004 J. Appl. Phys. 96 3467

- [8] Yeo Y-C 2004 Thin Solid Films **462-463** 34

- [9] Cabral C Jr., Lavoie C, Ozcan A S, Amos R S, Narayanan V, Gusev E P, Jordan-Sweet J L and Harper J M E 2004 J. Electrochem. Soc. **151** F283

- [10] Deegan T and Hughes G 1998 Appl. Surf. Sci. 123/124 66

- [11] Chandra S V J, Fortunato E, Martins R, Choi C J 2012 Thin Solid Films 520 4556

- [12] Cardarelli F 2008 Materials Handbook: A Concise Desktop Reference 2nd ed. (London: Springer)